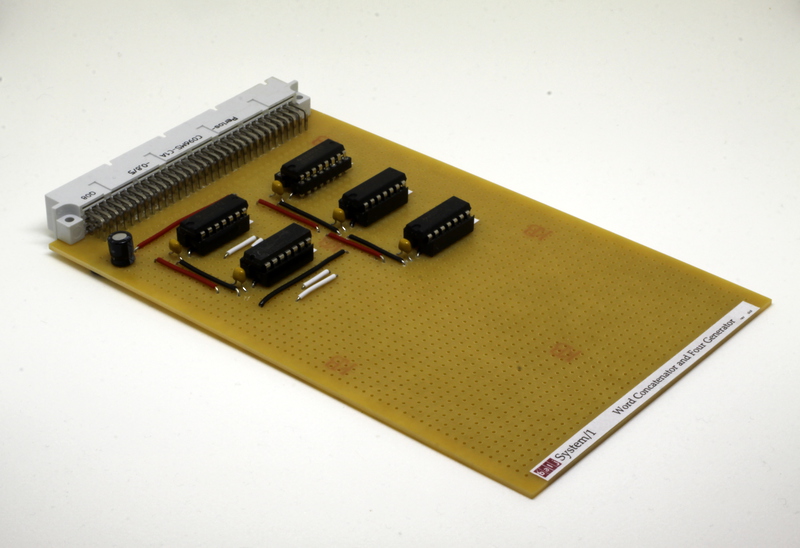

Word Concatenator and Four Generator

This board combines two very simple sections of System/1's design — the 'four generator', which emits a constant stream of fours, and the 'word concatenator', which glues together the bottom half of two 32-bit values to form its result.

The Four Generator

System/1 sometimes needs to use a constant value of 4 for internal operations; most notably, the first stage of the execution cycle loads the current value of the program counter into the MAR whilst simultaneously adding four to it, to address the next instruction. A less-important use is in the interrupt handling; when entering interrupt context, System/1 loads the alternate program counter with 0x00000004, making this effectively a hard-coded interrupt vector.

The implementation is straightforward; since the output needs to be a 1 solely during the third phase of the 'bit' clock, it just requires a simple 'CP=0b00010' computation. Half of a 74HC02 quad-NOR tests the CP0 and CP2-4 signals, and a third of a 74HC11 triple-3AND combines those two outputs with CP1 to generate the final FOUR_OUT result.

(No, I'm not sure why I chose to use a 74HC11 instead of half of a 74HC08 — it halves the gate delay, but that's hardly going to be particularly important here!)

The Word Concatenator

This half of the board is rather less important, and in fact could be regarded as pretty redundant; the complete system will include a shifter, after all, so any dedicated 'concatenate r0, r1 into r2' instruction can generally be replaced by a 'shift r1 by 16 into r2; or r0, r2 into r2' sequence instead. However, since System/1's instruction encoding only supports a 16-bit immediate field, 32-bit immediate values need to be loaded in two halves and glued together somehow, and having dedicated support for it seemed like a good idea.

(My original notes have an explicit 'concatenate' opcode, taking two source registers and a destination register; however, on further thought I'm wondering how difficult it would be to add a 'load immediate high-word' instruction, reminiscent of Alpha's ldah... They also use the term 'overlay' instead of 'concatenate', because I really have no idea what to call this thing.)

The implementation is again pretty simple — two 74HC164s registers are used to store the low 16 bits of whatever's on the B bus whilst a 74HC157 data selector, driven by CP4 (the high bit of the clock phase counter), passes the data from the A bus straight through to OVERLAY_OUT. As soon as CP4 goes high, during bits 16-31, the data selector switches to put the delayed value from the B bus (which has just started falling out of the shift register) on the output instead. Job done!

Related Build Log Entries

- 28th September, 2014 (backdated) - Fourgen and concat build